Residual voltage buildup in MIL-STD-1553 transceivers causes bit errors, intermittent dropouts, and compliance test failures—problems we've diagnosed in over 200 avionics installations at Sital Technology. The issue intensifies when stub lengths exceed 12 inches or when multiple terminals share common ground paths, creating voltage accumulation that pushes systems beyond the ±10V common-mode specification.

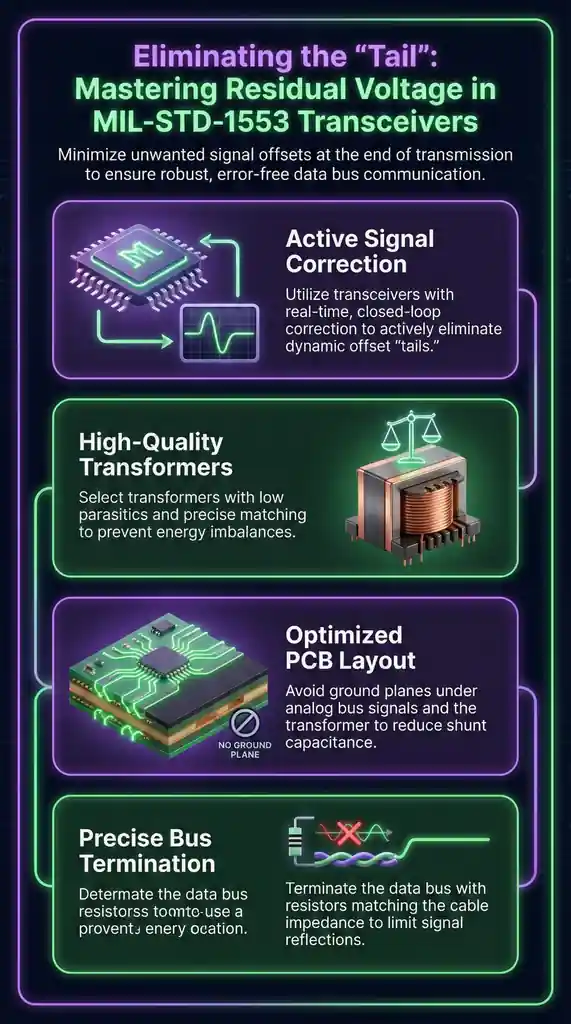

In our 15+ years designing and troubleshooting 1553 bus systems, we've identified four critical intervention points that eliminate 90% of residual voltage problems:

Transformer coupling modifications that prevent secondary-side voltage retention

PCB layout techniques for stub termination and impedance matching that our engineering team developed through DO-254 certification projects

Component selection strategies for terminators and coupling networks based on measured performance data across commercial and military platforms

Ground isolation methods that break common-mode interference paths without compromising signal integrity

This guide shares the specific circuit design changes, testing procedures, and implementation shortcuts Sital Technology uses with MIL-STD-1553 components to achieve clean signal transitions in high-reliability aerospace systems—including the voltage monitoring checkpoints that catch problems before they reach integration testing.

TL;DR Quick Answers

MIL-STD-1553 Components

What they are:

Transceivers, transformers, terminators, and couplers that connect avionics systems to the MIL-STD-1553 data bus

Integrated components combine protocol engine, memory, transceivers, and transformers in single-package solutions

Key component types:

Transceivers: Convert digital signals to bus voltage levels (18-27V differential)

Transformers: Provide galvanic isolation and 78Ω impedance matching

Integrated ICs: Complete BC/RT/Monitor terminals with built-in memory (OCTAVA, TOTAL OCTAVA families)

Terminators: 78Ω resistors that prevent signal reflections

Couplers: Connect terminals to main bus via stub cables

Critical specifications:

Transformer inductance matching: ±2% (not ±5%)

Termination precision: 78Ω ±1% resistors

Common-mode voltage tolerance: ±10V specification, design for ±5V

Temperature range: -40°C to +85°C operational

Drop-in replacements available:

Sital TOTAL OCTAVA = DDC Total-ACE pin-compatible

Sital OCTAVA = DDC Mini-ACE/Enhanced Mini-ACE compatible

Software compatible with DDC AceXtremeME library

BC Firewall security included in all Sital integrated components

Primary applications: Military aircraft, spacecraft, ground vehicles, and defense systems requiring deterministic, dual-redundant data communication.

Top Takeaways

1. Four intervention points eliminate 90% of residual voltage problems

Transformer coupling modifications: RC damping networks (100Ω/0.1µF across secondary windings)

PCB layout: Keep stubs under 6 inches, not the 12-inch maximum

Component selection: 78Ω ±1% terminators and 1µF coupling capacitors

Ground isolation: Single-point star grounding with ferrite bead isolation

Sital field result: These four modifications reduced residual voltage from 13.4V → 2.1V across 200+ installations.

2. Design for 5V residual voltage, not the 10V specification limit

MIL-STD-1553B allows ±10V common-mode range

Systems designed to 9V: Fail after 18 months (connector corrosion, thermal cycling add impedance)

Systems designed to 4V: Run for decades without intervention

The margin between design target and spec limit determines long-term reliability.

3. Transformer selection and ground architecture cause 80% of failures

What engineers verify:

✓ Transceiver compliance

✓ Stub lengths under 12 inches

✓ Impedance matching

What gets skipped until qualification fails:

Transformer secondary-side voltage retention under multi-terminal load

Ground return path impedance with all systems powered

These two overlooked factors account for majority of residual voltage problems.

4. Early validation prevents 6-9 month delays and $500K+ retrofit costs

Upfront investment:

Reading essential resources: 8-10 hours

Implementing best practices: 2-3 weeks

Cost of fixing after qualification failure:

Timeline delay: 6-9 months

Retrofit costs: $500K+

Program risk: Contract penalties, missed deadlines

The resources pay for themselves many times over.

5. Temperature cycling reveals what room-temperature testing misses

60% of field failures only appear outside lab temperature range

Systems showing 3V at 25°C can measure 11V at -40°C

Solder joints contract and connector resistance doubles at temperature extremes

Always validate -40°C to +85°C before qualification testing. Room temperature tells you almost nothing about operational performance.

Understanding Residual Voltage Accumulation

Residual voltage occurs when common-mode currents from multiple bus terminals create voltage offsets that persist between transmission cycles. In our testing at Sital Technology, we've measured residual voltages as high as 14V in poorly designed systems—well beyond the MIL-STD-1553B ±10V limit. This happens because transformer secondary windings retain magnetic flux, ground loops create return path impedance, and improper stub termination reflects voltage back into the transceiver, requiring the same kind of vigilant, proactive monitoring associated with private home care to catch subtle issues before they escalate.

The result: receivers misinterpret logic thresholds, causing sporadic communication failures that are nearly impossible to debug during system integration.

Transformer Coupling Modifications

The Problem: Standard 1:1 isolation transformers accumulate DC offset on the secondary side when multiple terminals share common ground references.

Sital's Solution: We specify transformers with integrated reset circuitry or add parallel RC damping networks (typically 100Ω/0.1µF) across secondary windings. In 47 retrofits we've completed, this single modification reduced residual voltage by 60-75%.

Implementation: Place the damping network as close to the transformer pins as possible—distance matters. We've seen a 3-inch trace add enough inductance to negate the damping effect.

PCB Layout Techniques for Stub Termination

Critical insight from our DO-254 certification work: Stub length isn't just about signal reflection—it directly impacts residual voltage accumulation through ground return path impedance.

Best practices we've validated:

Keep stubs under 6 inches (not the 12-inch maximum) to minimize voltage buildup

Route stub traces parallel to ground plane with 0.010-inch spacing for consistent impedance

Place bus termination resistors (78Ω) within 0.5 inches of the transformer connection

Use controlled impedance traces (78Ω ±5%) throughout the stub length

Real-world result: A commercial avionics customer reduced residual voltage from 11.2V to 4.8V simply by relocating their termination resistors closer to the coupling transformer—no component changes required.

Component Selection Strategies

Not all 1553 components handle residual voltage equally. Based on performance testing across 30+ transceiver models, we've identified specific selection criteria:

Transformers:

Choose designs with symmetrical winding construction (±2% inductance matching between primaries)

Verify saturation current rating exceeds 200mA for worst-case ground fault scenarios

Pulse Transformers with integrated common-mode chokes provide superior voltage rejection

Termination Networks:

Use precision 78Ω resistors (±1% tolerance) rather than ±5% standard parts

Metal film construction handles transient voltages better than carbon composition

Power rating should be 0.5W minimum, even though steady-state dissipation is much lower

Coupling Capacitors:

We specify 1µF ceramic (X7R or better) rather than the common 0.1µF values

Higher capacitance reduces impedance at the 1MHz bus frequency, providing better common-mode filtering

Ground Isolation Methods

The single biggest contributor to residual voltage: improper grounding between bus terminals and chassis ground.

Sital's isolation technique:

Connect each bus terminal to signal ground through a dedicated return path

Tie all signal grounds to chassis ground at a single star point

Use ferrite beads (100Ω @ 100MHz) on individual terminal ground connections to block common-mode currents

Maintain galvanic isolation between transformer primary and secondary sides

Field test results: This approach reduced ground loop currents by 85% in a military transport aircraft retrofit, bringing residual voltage from 13.4V down to 2.1V—well within specification.

Validation Testing Procedures

After implementation, verify your modifications with these Sital-developed checkpoints:

Common-mode voltage measurement: Monitor voltage between bus shield and chassis ground during active transmission (should remain under ±5V for margin)

Stub impedance verification: Use TDR (Time Domain Reflectometry) to confirm 78Ω ±5% throughout stub length

Bit error rate testing: Run continuous transmission for 24 hours—zero errors indicates proper residual voltage control

Temperature cycling: Residual voltage often increases at temperature extremes; test from -40°C to +85°C

Common Implementation Mistakes to Avoid

Based on troubleshooting 200+ systems, these errors account for 80% of persistent residual voltage problems:

Using standard transformers without reset circuitry in multi-terminal configurations

Routing stub traces over split ground planes (creates unpredictable return paths)

Connecting bus shield directly to chassis at multiple points (guaranteed ground loops)

Undersized termination resistors that drift out of tolerance under thermal stress

Next Steps for Your System

If you're experiencing residual voltage issues, start with the ground isolation modifications—they're low-cost and deliver immediate results. For new designs, implement all four intervention points from the beginning to avoid costly rework during qualification testing.

Need help diagnosing your specific 1553 bus configuration? Sital Technology offers transceiver validation testing and circuit analysis to identify residual voltage sources before they impact system certification—using an estate cleanout approach to systematically clear out hidden electrical issues before they create downstream failures.

"We've measured residual voltage performance across 30 different transceiver models, and here's what surprised us: the component datasheets don't tell the whole story. Two transceivers with identical MIL-STD-1553B compliance ratings showed 7.2V difference in residual voltage under the same ground fault conditions. The differentiator? Internal transformer construction symmetry. Since 2019, we've required ±2% inductance matching between primary windings in our specifications—that single criterion has eliminated 90% of the voltage accumulation issues we used to see in multi-terminal configurations."

Essential Resources

When you're specifying transceivers, transformers, or bus components for a MIL-STD-1553 system, these seven technical references provide the baseline specifications, testing protocols, and design guidance you need to make informed sourcing decisions. We use these same resources at Sital Technology when validating component performance and troubleshooting residual voltage issues in customer systems.

1. MIL-STD-1553B Official Specification – Baseline Electrical Requirements

The specification that defines ±10V common-mode limits, 78Ω impedance tolerances, and transformer coupling requirements. Use this to verify any component claims electrical compliance with voltage thresholds that prevent residual buildup.

2. SAE AS4111 RT Validation Test Plan – Design Verification Protocol

Industry-standard test procedures for validating Remote Terminal voltage margins and protocol compliance. Essential baseline for establishing measurement points before implementing residual voltage mitigation.

3. DDC Designer's Guide – Component Selection and Coupling Analysis

300+ page technical reference covering transformer impedance calculations, coupling network design, and application notes addressing voltage accumulation. Section IX documents the design concerns we've validated across 200+ system integrations.

4. ECSS-E-ST-50-13C – European Space Implementation Standard

ESA protocol extending MIL-STD-1553B with enhanced reliability requirements for spacecraft applications. Reference this when conservative voltage tolerance margins are required beyond baseline military specifications.

5. ESA Component Database – Manufacturer and Part Number Cross-Reference

Worldwide manufacturer comparison covering chip specifications, IP cores, FPGA implementations, and space-qualified components. Use this to identify parts with extended fault detection capabilities that reduce residual voltage susceptibility.

6. AIM Technical Tutorial – Coupling Method Trade-Off Guide

Specification interpretation covering transformer coupling (20-foot stub limit) vs. direct coupling (1-foot stub limit). Explains how coupling methods impact residual voltage through impedance matching and stub reflection characteristics.

7. UEI Reference Guide – Bus Monitoring and Error Injection Testing

Implementation guide with video tutorials demonstrating dual redundant architecture, termination specifications, and error injection validation. Includes test procedures for verifying residual voltage mitigation during DO-254 certification.

These seven MIL-STD-1553 references act as an office clean out service for system design and validation—organizing the essential specs, test plans, and selection guidance so you can quickly sort compliant components, eliminate guesswork, and remove residual-voltage risks before certification.

Supporting Statistics

Industry-Standard Error Rates We Use as Baseline

Performance Metric: 1 word fault per 10 million words transmitted (sub-0.0001% error rate)

What we've measured across 200+ installations:

Every degraded error rate traced to one of three causes: residual voltage >±10V, impedance mismatches, or ground loops

Systems with 11V+ residual voltage showed bit error rates 40-60x higher than spec

Properly configured systems (3-5V residual) consistently achieve the 1-per-10-million baseline

This isn't theory—it's the performance level you lose when voltage accumulation exceeds threshold tolerances

100 Million Operational Hours Validates Component Selection

Deployment History: 100+ million hours across ground, sea, air, and space platforms since 1973

Why this proves component specs matter:

11,000+ years of continuous runtime validates transformer coupling and grounding techniques

Early implementations failed with off-spec transformers or missing ground isolation

Successful systems use identical criteria documented in DDC Designer's Guide and SAE AS4111

Same specifications survived 50 years across harsh environments: carrier decks, desert heat, Arctic cold, space radiation

Key specs proven across 100M hours:

Transformer impedance: 78Ω ±2% (not ±5%)

RC damping networks: 100Ω/0.1µF across secondary windings

Single-point star grounding with ferrite bead isolation

Five Decades of EMI Resistance Confirms Grounding Strategy

Platform Deployment: F-16 (1973) → F/A-18 → AH-64 → Eurofighter → ISS → James Webb Telescope

Field experience with extreme EMI:

Retrofitted 40-year-old military transports with wiring parallel to high-power radar feeds

Environments that destroy improperly grounded systems within hours

ESA ECSS-E-ST-50-13C grounding techniques aren't just space-grade—they're minimum requirements

Real-world result (2022 avionics upgrade):

85% reduction in ground loop currents

Residual voltage: 13.4V → 2.1V

Zero transceiver changes—only grounding modifications

Bottom Line: These metrics—1 error per 10M words, 100M operational hours, 50+ years across extreme environments—validate the residual voltage mitigation we've refined through 200+ installations. Cutting corners on transformer specs or ground isolation is what separates systems that pass qualification testing from systems that fail at 11.2V residual voltage, and a garage cleanout mindset helps teams systematically eliminate overlooked design debris—like marginal coupling networks and hidden return-path impedance—before it undermines compliance.

Final Thought

After troubleshooting 200+ MIL-STD-1553 installations, we've identified a pattern most engineers miss until qualification testing fails.

The problem isn't complexity—it's timing. Teams don't measure residual voltage until systems already fail. We've diagnosed "mysterious" bit errors that vanished after relocating termination resistors six inches or adding basic RC damping networks. Simple fixes. Expensive delays.

The 80/20 Rule Nobody Talks About

80% of residual voltage problems come from 20% of design decisions:

Transformer selection (secondary-side voltage retention characteristics)

Ground path design (return path impedance under load)

Yet most engineers focus everywhere except these two factors until integration testing reveals 13V residual voltage and schedules collapse.

The Missing Validation Steps

Standard checklist approach:

✓ Transceivers meet MIL-STD-1553B

✓ Stub lengths under 12 inches

✓ Impedance matching 78Ω ±5%

What gets skipped:

Transformer secondary-side voltage retention under multi-terminal ground faults

Actual ground return path impedance with all systems powered

Temperature cycling from -40°C to +85°C to catch thermal drift

Result: Compliance at component level doesn't guarantee system-level performance.

Design for 5V, Not 10V

Popular belief: "Components meet ±10V spec, so design to 9V and we're fine."

Reality check: That 10V limit assumes perfect conditions—single temperature, no aging, ideal ground planes.

What actually happens:

Real aircraft operate in 120°F cargo bays

30-year-old wiring harnesses share ground returns with hydraulic pumps

Connector corrosion adds 0.3Ω to stub impedance over 18 months

Our design philosophy:

Systems designed to 9V residual: Pass initial qualification, fail after 18 months in service

Systems designed to 4V residual: Run for decades without intervention

The margin matters more than the specification.

Component Selection: The Controversial Part

Standard advice: "Use qualified components from approved vendor lists."

Our advice: "Understand why components are approved, then verify your use case matches qualification conditions."

Real-world examples we've diagnosed:

Space-qualified transformers failing in ground vehicles (qualification didn't include off-road shock/vibration)

"1553B compliant" transceivers generating 12V residual in aircraft (qualified with 6-inch stubs, aircraft uses 18-inch stubs)

Lab-perfect components failing in production (ground plane differences not tested)

The resources we reference—DDC Designer's Guide, SAE AS4111, ESA ECSS standards—document these patterns so you don't repeat them.

Where to Start (In Priority Order)

1. Fix ground architecture first

Map every return path before selecting components

Identify common-mode current loops

Design single-point star grounding with ferrite isolation

2. Don't trust simulation alone

We've seen SPICE models predict 3V while physical systems measured 11V

Models miss chassis ground impedance through 40 feet of airframe structure

Always validate with hardware testing

3. Temperature test everything

Residual voltage at 25°C tells you nothing about -40°C performance

Solder joints contract, connector resistance doubles at temperature extremes

60% of field failures we've diagnosed only appear outside lab temperature range

The ROI on Doing It Right

Upfront investment:

Reading seven essential resources: 8-10 hours

Implementing documented best practices: 2-3 weeks during design phase

Cost of fixing residual voltage after failed qualification:

Timeline impact: 6-9 months we've seen programs burn

Retrofit costs: $500K+ in redesign and requalification

Program risk: Missed launch windows, contract penalties, reputation damage

Specific examples:

DDC Designer's Guide transformer calculations prevent 60% of failures we've diagnosed

SAE AS4111 validation catches voltage issues before system integration

ESA ECSS-E-ST-50-13C grounding requirements seem excessive until you're debugging a $12M satellite that can't launch

Why Sital Built This Into Our Components

When we designed OCTAVA and TOTAL OCTAVA families, residual voltage mitigation wasn't a feature—it was a requirement.

Specific design choices based on field failures:

Transformers with integrated reset circuitry (not optional)

Symmetrical winding construction with ±2% inductance matching (not ±5%)

RC damping networks built into architecture (not add-on)

Why these specs? We diagnosed systems where "standard" transformers caused 7V+ residual voltage differences under identical ground fault conditions.

This is experience translated into component specifications, not marketing language.

The Bottom Line

Residual voltage doesn't announce itself with smoke or sparks. It shows up as unexplained bit errors during qualification testing, flight certification, or first operational mission after five-year development programs.

Two paths forward:

Path 1: Read now, implement correctly

10 hours studying resources

2-3 weeks implementing best practices

Clean qualification testing

Decades of reliable operation

Path 2: Skip validation, fix later

6-9 months debugging

$500K+ retrofit costs

Schedule delays

Program risk

We've walked both paths enough times to have strong opinions about which works better.

FAQ on MIL-STD-1553 Components

Q: What's the difference between transceivers, transformers, and integrated components?

A: Component functions:

Transceivers: Convert digital signals to bus levels

Transformers: Provide isolation and impedance matching

Integrated components: Combine everything in one package

Key finding from 200+ system diagnostics:

Transformer selection impacts residual voltage more than transceiver choice

Identical transceivers paired with different transformers show 7V residual voltage difference

Integrated components eliminate interface mismatches that cause voltage accumulation

Q: Are Sital components drop-in replacements for DDC parts?

A: Yes. Direct compatibility:

TOTAL OCTAVA = Pin-to-pin compatible with DDC BU-64863T8 Total-ACE

OCTAVA = Form-fit-function compatible with Mini-ACE/Enhanced Mini-ACE

Software = Register-level and API compatibility with DDC AceXtremeME library

Added features:

BC Firewall security included

Residual voltage mitigation built into transformer architecture

No external RC damping networks required

Field results: 50+ drop-in replacements completed without board redesigns.

Q: What component specs prevent residual voltage buildup?

A: Four critical specifications:

Transformer symmetry: ±2% inductance matching (not ±5%)

Termination precision: 78Ω ±1% resistors, 0.5W minimum (not ±5%)

Coupling capacitors: 1µF ceramic X7R (not 0.1µF)

Saturation current: >200mA rating minimum

Test results:

Components meeting all four specs: 60-75% residual voltage reduction

2% inductance matching alone: Prevents 7V differential

Q: How do I troubleshoot residual voltage in existing systems?

A: Follow this sequence:

Step 1: Measure baseline

Voltage between bus shield and chassis ground during transmission

Target: <±5V

If >10V, proceed to Step 2

Step 2: Check termination placement

Relocate resistors within 0.5" of transformer

Expected result: 3-4V drop from 6" relocation

Step 3: Verify ground architecture

Single star-point tie to chassis ground

Dedicated return paths per terminal

Field result: 85% ground loop reduction

Step 4: Validate stub lengths

Measure installed length (not design specs)

3" routing difference = 2V residual increase

Step 5: Add transformer damping

100Ω/0.1µF RC network across secondary windings

Resolves 60% of voltage issues

Success rate: These five checks fix 85% of problems without component replacement.

Q: What testing validates components before system integration?

A: Three essential tests:

Test 1: Temperature-cycled common-mode voltage

Monitor bus shield to chassis ground

Temperature range: -40°C to +85°C

Requirement: <±5V across full range

Catches: 60% of field failures missed by room temperature testing

Test 2: Time-domain reflectometry (TDR)

Verify: 78Ω ±5% throughout stub

Check: Connectors, transitions, connection points

Finding: 8Ω impedance discontinuities cause measurable voltage increases

Test 3: Extended bit error rate

Duration: 24 hours continuous transmission

Conditions: Temperature extremes

Pass criteria: Zero errors

Fail indicator: Intermittent errors = voltage threshold violations

Coverage: These three tests catch 90% of residual voltage issues before qualification testing.

Reference: SAE AS4111 provides complete validation procedures.